## PARALLEL SYSTEMS LABORATORY: ACCESS, ALLOCATION, AND CONTROL DEFENSE ADVANCED RESEARCH PROJECTS AGENCY

## FINAL TECHNICAL REPORT

June 30, 1992

Principal Investigator: Leonard Kleinrock

This document has been approved for public release and sale; its distribution is unlimited.

> Computer Science Department School of Engineering and Applied Science University of California Los Angeles

## PARALLEL SYSTEMS LABORATORY: ACCESS, ALLOCATION, AND CONTROL DEFENSE ADVANCED RESEARCH PROJECTS AGENCY

이 혼자는 것 한 것 같아. 것 같아.

· . ¬

## FINAL TECHNICAL REPORT

June 30, 1992

Principal Investigator: Leonard Kleinrock

Computer Science Department School of Engineering and Applied Science University of California Los Angeles

| Unc] | lassi | lfied |  |

|------|-------|-------|--|

|      |       |       |  |

| REPORT DOCUMENTATION PAGE                                           |                             | READ INSTRUCTIONS<br>BEFORE COMPLETING FORM                    |

|---------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------|

|                                                                     |                             | 3. RECIPIENT'S CATALOG NUMBER                                  |

|                                                                     |                             |                                                                |

| 4. TITLE (and Sublitio)                                             |                             | S. TYPE OF REPORT & PERIOD COVERED                             |

| PARALLEL SYSTEMS LABORATORY: ACCE                                   | SS, CONTROL,                | Final Technical Report                                         |

| AND ALLOCATION                                                      |                             | July 1, 1987 - June 30,1992                                    |

| Final Technical Report                                              |                             | 6. PERFORMING ORG. REPORT NUMBER                               |

| 7. AUTHOR()                                                         |                             | B. CONTRACT OR GRANT NUMBER(s)                                 |

|                                                                     |                             |                                                                |

| Leonard Kleinrock                                                   |                             | MDA 903-87-C-0663                                              |

|                                                                     |                             |                                                                |

| 9. PERFORMING ORGANIZATION NAME AND ADDRESS                         |                             | 10. PROGRAM ELEMENT, PROJECT, TASK<br>AREA & WORK UNIT NUMBERS |

| School of Engineering & Applied S                                   |                             |                                                                |

| University of California, Los Angeles<br>Los Angeles, CA 90024-1596 |                             | DARPA Order No. 2496/28                                        |

| 11. CONTROLLING OFFICE NAME AND ADDRESS                             |                             |                                                                |

| Defense Advanced Research Project                                   | s Agency                    | June 30, 1992                                                  |

| 3701 N. Fiarfax Drive                                               | ~ ·                         | 13. NUMBER OF PAGES                                            |

| Arlington, VA 22203-1714                                            |                             |                                                                |

| 14. MONITORING AGENCY NAME & ADDRESS(If different                   | from Controlling Office)    | 18. SECURITY CLASS. (of this report)                           |

|                                                                     |                             |                                                                |

|                                                                     |                             | 18- DECLASSICATION/DOWNGRADING                                 |

|                                                                     |                             | 154. DECLASSIFICATION/DOWNGRADING<br>SCHEDULE                  |

| 16. DISTRIBUTION STATEMENT (of this Report)                         |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     | . D. Lasana Diat            |                                                                |

| Approved for Publi                                                  | c Kelease: Dist             | ribution Unlimited                                             |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

| 17. DISTRIBUTION STATEMENT (of the abotract entered in              | : Black 20, if different ke | n Report)                                                      |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

| IS. SUPPLEMENTARY NOTES                                             |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

| 19. KEY WORDS (Continue on reverse side if necessary and            | Identify by block number)   |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

| 20. ABSTRACT (Continue on reverse side il necessary and i           | igeniity ay steek nubeet)   |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

|                                                                     |                             |                                                                |

SECURITY CLASSIFICATION OF THIS PAGE (Then Date Entered)

SECURITY CLASSIFICATION OF THIS PAGE (Then Date Entered)

5/H 0102- LF- 014- 4401

ALC: NAME OF A DESCRIPTION

SECURITY CLASSIFICATION OF THIS PASE(Then Date Entered)

## PARALLEL SYSTEMS LABORATORY: ACCESS, ALLOCATION, AND CONTROL

## FINAL TECHNICAL REPORT

June 30, 1992

Contract Number: MDA 903-87-C-0663 DARPA Order Number: 2496/28 Contract Period: July 1, 1987 to June 30, 1992 Report Period: July 1, 1987 to June 30, 1992

Principal Investigator: Leonard Kleinrock

(310) 825-2543

Computer Science Department School of Engineering and Applied Science University of California, Los Angeles

Sponsored by

## **DEFENSE ADVANCED RESEARCH PROJECTS AGENCY**

The views and conclusions contained in this document are those of the authors and should not be interpreted as necessarily representing the official policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the United States Government.

## PARALLEL SYSTEMS LABORATORY: ACCESS, ALLOCATION, AND CONTROL

Defense Advanced Research Projects Agency

Final Technical Report

June 30, 1992

This Final Technical Report covers research carried out by the Parallel Systems Laboratory: Access, Allocation and Control at UCLA under DARPA Contract Number MDA 903-87-C-0663, covering the period July 1, 1987 through June 30, 1992.

Below we restate the tasks which have been the subject of this research effort. We then give a summary of the salient results of this research in capsule form which is followed by an extensive list of publications, dissertations and theses which have been the result of this research. The contract period covered is from July 1, 1987 to June 30, 1992; however, one must note that whereas this contract formally ended on June 30, 1992, the period from July 1, 1990 to June 30, 1992 was simply a no-cost extension of funds to complete and publish results of studies that had begun during the main contract period.

The included papers summarize a number of our research activities but are only a sample of our work. Of course the more complete results are contained in the full set of publications we have listed, copies of which have been sent to the DARPA contracting office during the period of this contract.

## **Brief Statement of Work**

The brief statement of work which describes the tasks on which we have been working during this contract are as follows:

TASK I. FUNDAMENTAL TOOLS AND ISSUES IN PARALLEL PROCESSING SYSTEMS

It is imperative that we develop evaluation tools as well as fundamental understanding of the behavior, performance and tradeoffs for parallel processing systems. We propose to develop such tools, and to evaluate the way in which the system resources interact with each other and with the demands placed upon them.

#### TASK II. PARALLEL PROCESSING ARCHITECTURE AND ALGORITHM DESIGN

A given set of resources can be configured to be centralized or distributed in many ways. We propose to study the effect on performance and cost of various system topologies (e.g., series, parallel, series/parallel, network), organization and architecture. We will design algorithms to operate in a parallel processing environment and will evaluate the effect of unreliable processors.

## TASK III. MIGRATING AND ADAPTIVE PROCESSES

The distributed control of parallel systems has proven to be a major development in system design. We propose to study the design of distributed algorithms which adapt to the load and structure of their environment, and to evaluate their performance (delay, efficiency, complexity) in massively connected systems.

## TASK IV. DISTRIBUTED DATA BASE

The coordination of a data base in a distributed environment is an extremely important issue in large systems today. We propose novel methods for accessing and updating data base systems from distributed sources using the technique of optimistic locking; this algorithm has the potential for providing higher efficiency in a variety of complex systems.

#### TASK V. TIGHTLY COUPLED PARALLEL PROCESSING SYSTEMS

Tightly coupled processors in a parallel processing environment may suffer serious performance degradation problems. We propose to provide tools for evaluating performance for a very wide class of parallel processing systems. We will include the effect of the number of processors available, the parallelism inherent in various graph models of computation, the arrival process of new jobs, and the randomness in the task computation times. A related issue is that of massive connectivity in massively parallel systems. We propose to evaluate the tradeoff among communications, processing and storage in these systems.

#### TASK VI. EXPERIMENTATION IN PARALLEL SYSTEMS

A key task in this project is to conduct a carefully staged sequence of experiments in parallel processing using the existing testbeds available in the Computer Science Department at UCLA. We have named this the Benevolent Bandit Laboratory (or BBL Project, for short). Our main purpose is to use it as a vehicle for experimenting with an operational parallel processing system; initially, we intend to use it to harness the power of underutilized workstations which, fortunately, are already connected together as a "system" through a local area network.

#### **Brief Summary of Significant Results**

During this contract period, we have published 21 papers and have had 2 additional papers accepted in professional journals. Moreover, we have contributed 2 book chapters. In addition to all of this, 6 Ph.D. students have graduated as a result of the work they have conducted under this research in addition to 6 Master's students.

Our major results fall into three somewhat overlapping areas which relate to the statement of work. These three areas are:

- 1. Parallel processing systems;

- 2. Distributed processing systems;

- 3. Distributed communications

In the area of parallel processing systems, we have a number of interesting results and developments. One of our major activities during this contract period was to develop what we call the Benevolent Bandit Laboratory; this is a testbed for understanding the behavior of distributed algorithms in an environment in which we recapture the idle processing capacities from a large number of workstations connected in a local area network. The concept here of course is to try to take advantage of the enormous amount of idle time experienced by most workstations. Indeed we built a shell around the workstation operating system which senses when the processor is idle for more than a minimum amount of time at which time our Benevolent Bandit shell takes over the processor and runs a background process; as soon as the user of the system needs access to his own workstation, the shell immediately relinquishes control and returns it to the user. We implemented the system, we measured it, we wrote and ran applications on it, and we analyzed the behavior of this system and of a large number of other similar systems of much greater extent both in numbers and operations. Indeed the paper by Kleinrock and Korfhage "Collecting Unused Processing Capacity: An Analysis of Transient Distributed Systems" which is included in the Appendix of this report summarizes the analytical results which we obtained for this system. The bottom line for such an operation is that one can capture the unused capacity of networked workstations and that the performance is predictable and understandable.

Another major development we achieved in our study of parallel processing systems was to understand how many processors one should use in order to effectively carry out the dependent tasks of a sequence of jobs as they flow into a parallel processing system with P processors. The problem here is if we have too many processors, the efficiency of each is low (but the response time is conveniently short); on the other hand, if we have too few processors, the efficiency of each is high (but the response time degrades). Using a combined objective function known as power, which is simply the ratio of efficiency to mean response time, we determine the optimal number of processors one should use in such a system, determine the optimum load such a system should sustain, and identify the principles of operation and insights which come out of such an analysis. The key ideas here are summarized in the paper by Kleinrock and Huang entitled "On Parallel Processing Systems: Ahmdal's Law Generalized and Some General Results on Optimal Design" included here in the Appendix of this report.

A third major thrust which was begun toward the end of this contract period was to study the behavior of asynchronous distributed processing in a moderately tightly coupled parallel processing system. In particular, the notion of decomposing a job into a number of parallel tasks, each one of which runs on a separate processor, but each one of which is not totally independent of the others was analyzed in some preliminary studies. There are two ways to run such a system: asynchronously (the method we favor) and synchronously (a more conservative approach). We have compared the maximum improvement available for asynchronous operation versus synchronous operation in the paper by Felderman and Kleinrock "An Upper Bound on the Improvement of Asynchronous vs. Synchronous Distributed Processing" and found that the gains were clearly predictable and of some significance. Furthermore, we analyzed the details of a specific two-processor system in the paper by Kleinrock "On Distributed Systems Performance" and gave an exact analysis of the behavior of this system, demonstrating the speedup possible in such an environment. Both these papers are included in the Appendix.

In addition a number of studies involving other aspects of parallel processing systems was studied and reported upon. For example we determined the algorithms for performing optimal parallel merging and sorting using a limited number of processors in an efficient fashion. We also took advantage of broadcast communications in such sorting algorithm problems. Certain aspects of load sharing in limited access distributed systems were studied for a collection of loosely coupled parallel processors. Moreover, we studied the behavior of load sharing among a set of processors in a broadcast network; we found that if one balances the most heavily loaded processor with the most lightly loaded processor, significant gains can be had and it takes very few such pairs to be matched before the majority of the improvement is achieved; this occurs long before all processors are matched to share load thereby resulting in a very efficient load sharing at very low overhead. A related load sharing and load balancing study looked at a processing system as a "field" of processors which dynamically share load based on the immediate backlog; here again the effect of load sharing was shown both analytically and simulation-wise to be extremely effective.

Our second major area of research was in the field of distributed systems. This area covers a variety of systems models including the problems of multiaccess in broadcast communications systems, distributed database systems, and distributed search methods. Basically we have developed a number of advanced multiaccess schemes whose performance is found to be quite efficient and whose analyses have been carried out to give excellent predictions of their performance. These include schemes such as CSMA, random polling, hierarchical access schemes (which use random access in the lightly loaded portion of a network and reserved bandwidth in the more heavily used portions of a network), multiaccess in bus networks which approach gigabit speeds (thereby changing the latency vs. bandwidth bottleneck tradeoff), an analysis of access systems under dynamically changing loads, and the effect of the overhead of switching in some of these multiaccess systems. The general flavor here was to provide more effective analytic tools to be able to predict the performance of a variety of multiaccess schemes in a number of different scenarios.

We have also looked at distributed database systems using what is called optimistic concurrency control; specifically we are concerned with the performance of such systems as compared to the conservative locking schemes which are used in the more classical database control systems. We provided an analysis and simulation of optimistic concurrency control schemes and identified their effectiveness in a variety of different configurations. Lastly, in the area of distributed systems we developed and analyzed a tree search algorithm using parallel processors.

The third major area of our research involved distributed communications. This is a very rapidly growing area as we move into the domain of gigabit per second networks and the paper by Kleinrock entitled "ISDN - The Path to Broadband Networks" is included in the appendix of this report as a summary of some of out thinking and findings in this area. We are further looking into the details of congestion control in the LAN-to-LAN interconnect problem, and have made some preliminary studies of wavelength division multiplexing in optical networks. This discussion of wavelength division multiplexing has also been extended to the area of metropolitan area networks.

Overall our research progress has advanced in these many domains with considerable success in providing an understanding of the underlying behavior of parallel and distributed systems. We have created a number of evaluation tools for understanding these systems, we have studied the ways in which the algorithms and architectures behave with respect to each other and their impact upon each other, we have developed load balancing techniques and distributed database techniques along with their analyses, and have in general advanced the state of the art in order to provide a variety of tools, techniques, experimental measurements and implementations for the understanding of the behavior of parallel systems.

## PSL PUBLICATIONS DARPA CONTRACT

Computer Science Department University of California, Los Angeles Professor Leonard Kleinrock

July 1, 1987 - June 30, 1992

## **CHAPTERS IN BOOKS**

- 1. Kleinrock, L., "Performance Evaluation of Distributed Computer-Communication Systems", Chapter 1, *Queueing Theory and Its Applications*, O.J. Boxma and R. Syski (Eds.), North-Holland Elsevier Science Publishing Company, Inc., pp. 1-57, September 1988.

- 2. Gerla, M. and L. Kleinrock, "Flow Control Protocols", in *Computer Network Architec*tures and Protocols (Second Edition), Kenneth Schubach (Ed.), Plenum Publishing Corporation, New York, New York, pp. 265-320, May 1989.

### **Ph.D DISSERTATIONS**

- 1. Huang, J. H. "On the Behavior of Algorithms in a Multi-Processing Environment", October 1988.

- 2. Green, Joseph "Load Balancing Algorithms in Computer Networks", October 1988.

- 3. Mehovic, Farid "Performance Modeling of Concurrency Control", March 1989.

- 4. Korfhage, Willard R. "Distributed Systems and Transient Processors", August 1989.

- 5. Lin, Tzung-I "Performance Analysis of Finite-Buffered Multistage Interconnection Networks with Various Switching Architectures," December 1990.

- 6. Felderman, Robert E. "Performance Analysis of Distributed Processing Synchronization Algorithms," June 1991.

## **M. S. THESES**

- 1. Horng, Ming-Yun "An Analytic Model for Packet Flow in a Boolean N-Cube Interconnection Network", December 1987.

- 2. Schooler, Eve M. "Distributed Debugging in a Loosely-Coupled Processing System", February 1988.

- 3. Lin, Tzung-I. "An Analysis of State Restoration in Distributed Systems", March 1988.

- 4. Baker, Rusti "Distributed Simulation in the BBL Multicomputer System" January 1989.

- 5. Harinarayan Venkatesh, "Load Sharing In Limited Access Distributed Systems", 1990.

- 6. Chang, Chialin "Performance of LCFS Queueing Systems with Impatient Customers", June 1991.

## PUBLISHED PAPERS IN PROFESSIONAL AND SCHOLARLY JOURNALS

- 1. Kleinrock, L. and H. Levy, "On the Behavior of a Very Fast Bidirectional Bus Network", Proceedings of the IEEE International Conference on Communications (ICC '87), Vol. 3, No. 3, Seattle, Washington, June 7-10, pp. 1419-1426, 1987.

- 2. Felderman, R.E., "Extension to the Rude-CSMA Analysis", Correspondence item, *IEEE Transactions on Communications, Vol. COM-35, No. 8, pp. 848-849, August 1987.*

- 3. Gerla, M. and L. Kleinrock, "Congestion Control in Interconnected LAN's", *IEEE Network, Vol. 2, No. 1*, pp. 72-76, January 1988.

- 4. Ferguson, C. and R. Korf, "Distributed Tree Search and its Application to Alpha-Beta Pruning", AAAI '88 Proceedings, Vol. 1, pp. 128-132, August 1988.

- 5. Kleinrock, L. and Hanoch Levy, "The Analysis of Random Polling Systems" Journal of Operations Research, Vol. 36, No. 5, pp. 716-732, September-October 1988.

- 6. Felderman, R., E. Schooler, and L. Kleinrock, "The Benevolent Bandit Laboratory: A Testbed for Distributed Algorithms", *IEEE Journal on Selected Areas in Communica*tions, (JSAC), Vol. 7, No. 2 (ISSN 0733-8716), pp. 303-311, February 1989.

- 7. Akavia, G. and L. Kleinrock, "Hierarchical Use of Dedicated Channels", *Performance Evaluation, An International Journal, Vol. 9, No. 2, pp. 135-142, April 1989.*

- 8. Kleinrock, L. and W. Korfhage, "Collecting Unused Processing Capacity: An Analysis of Transient Distributed Systems" reprinted from, *Proceedings of the 9th International Conference on Distributed Computer Systems*, San Diego, June 5-9, 1989, for, *The Computer Society of the IEEE*, pp. 482-489, June 1989.

- 9. Felderman, R. and L. Kleinrock, "An Upper Bound on the Improvement of Asynchronous Versus Synchronous Distributed Processing", *The Society for Computer Simulation*, Distributed Simulation Conference 1990, David Nicol (Ed.), pp. 131-136, January 1990.

- 10. Bannister, Joseph and M. Gerla, "Design of the Wavelength-Division Optical Network", presented at *ICC'90*, Vol. 3, Sec. 323.2.1, pp. 962-967, Atlanta, GA., April 16-19, 1990.

- 11. Huang, J-H. and L. Kleinrock, "Optimal Parallel Merging and Sorting Algorithms Using

$\sqrt{N}$  Processors Without Memory Contention", *Parallel Computing*, Vol. 14, No. 1, pp. 89-97, May 1990.

- 12. Bannister, J.A., L. Fratta, and M. Gerla, "Routing in Large Metropolitan Area Networks Based on Wavelength - Division Multiplexing Technology" presented at the NATO Advanced Research Workshop on Architecture and Performance Issues of High-Capacity Local and Metropolitan Area Networks, Sophia Antipolis, France, June 25-27, 1990.

- 13. Kleinrock, L. "On Distributed Systems Performance", presented at the 7th ITC Specialist Seminar, Adelaide, 1989, Proceedings of the ITC Specialist Seminar, Paper No. 3.2, September 1990.

- 14. Kleinrock, L. and H. Levy, "On the Behavior of a Very Fast Bidirectional Bus Network", *IEEE Transactions on Communications*, Vol. 38, No. 10, pp. 1854-1862, October 1990.

- 15. Rosenberg, C., R. Mazumdar and L. Kleinrock, "On The Analysis of Exponential Queueing Systems with Randomly Changing Arrival Rates: Stability Conditions and Finite Buffer Scheme With a Resume Level", *Performance Evaluation*, Vol. 11, No. 4, pp. 283-292, November 1990.

- Huang, J.H. and L. Kleinrock, "Distributed Selectsort Sorting Algorithms on Broadcast Communication Networks," *Parallel Computing*, Vol. 16, No. 2 & 3, pp. 183-190, December 1990.

- 17. Felderman, R., and L. Kleinrock, "Two Processor Time Warp Analysis: Some Results on a Unifying Approach," *Advances in Parallel and Distributed Simulation*, Proceedings of the SCS Multiconference, Anaheim, CA, Simulation Series, Vol. 23, No. 1, pp. 3-10, January 23-25, 1991.

- 18. Kleinrock, L. "ISDN The Path to Broadband Networks", invited paper for *Proceedings* of the IEEE, Vol. 79, No. 2, pp. 112-117, February 1991 Special Issue on ISDN.

- 19. Harinarayan, V. and L. Kleinrock, "Load Sharing in Limited Access Distributed Systems," 1991 ACM Sigmetrics, Conference on Measurement and Modeling of Computer Systems, May 21-24, 1991, San Diego, CA.

- 20. Kleinrock, L. and J. H. Huang, "On Parallel Processing Systems: Amdahl's Law Generalized and Some Results on Optimal Design", invited paper for *IEEE Transactions on Software Engineering*, Special issue on Performance Evaluation Methodology, Vol.18, No.5, May 1992, pp.434-447.

- 21. Kleinrock, L. and F. Mehovic, "Poisson Winner Queues," *Performance Evaluation*, Vol. 14, No. 2, 1992, pp. 79-101.

#### PAPERS ACCEPTED FOR PUBLICATION

- 1. Levy. H. and L. Kleinrock, "Polling Systems with Zero Switch-Over Periods: A General Method for Analyzing the Expected Delay," accepted for publication in *Performance Evaluation*.

- 2. Huang, J.H. and L. Kleinrock, "Throughput Analysis and Protocol Design for CSMA and BTMA Protocols under Noisy Environment," accepted for publication in the *IEE Proceedings, Part I* UK, April 1991.

APPENDIX

12

EEE

The Computer Society of the IEEE 1730 Massachusetts Avenue NW Washington, DC 20036-1903

Washington • Los Alamitos • Brussels

HE NOT THE DE ELECTRICAL AND ELECTRONICS ENGINEERS INC.

## Collecting Unused Processing Capacity: An Analysis of Transient Distributed Systems

Leonard Kleinrock and Willard Korfhage<sup>\*</sup> Computer Science Department University of California, Los Angeles

#### Abstract

Distributed systems frequently have large numbers of idle computers and workstations. If these could be harnessed, then considerable computing power would be available at low cost. We analyze such systems using a very simple model of a distributed program (a fixed amount of work) to see how the use of transient processors affects the program's service time.

## 1 Networks of Transient Processors.

Networks of computers are fairly common in business and research environments throughout the world. Originally motivated by a desire to ease data and device sharing, many networks have grown in speed and sophistication to the point that distributed processing can be performed on them. These networks vary in size from a handful of personal computers on a low-speed network, to thousands of workstations and a variety of larger machines on a high-speed, fiber-optic network. A typical example is that of workstations on a highspeed, local area network in a research laboratory. Not only are there many machines, well connected by the network, but the users are likely to demand more and more computing power.

On these networks, we often have the situation that many of the personal computers and workstations are sitting idle, waiting for their users, and thus being wasted. If we could recover this wasted time for useful processing, then we would have considerable computing power available to us at low cost [6]. We refer to these processors, which are sometimes busy and sometimes not, as transient processors.

This situation has analogies to time-sharing. In the past, institutions had one large resource, a mainframe computer, that was shared by many users. As networks of workstations develop, the largest computing resource is no longer a single machine, but is instead the aggregate computing power of the workstations. In the same manner that it has been possible for many people to share a single machine, by using the idle time of one person to run the program of another, so it is now possible to share a network of workstations for large, distributed computations.

Whether this is technically feasible or not depends on a variety of factors, such as the characteristics of the communications medium, the characteristics of the computers, and the statistical characteristics of the user population. Mutka and Livny [13], and Nichols [14] have shown that under at least some circumstances, this is very practical and useful.

From an analytical point of view, we would like to have a queueing model of a network of transient processors executing distributed programs. In this paper we take a first step toward this end by analyzing the service time for a very simple model of a distributed program (a fixed amount of work) to see how the use of transient processors affects what would otherwise be a deterministic service process.

## 2 The Model.

Assume that we have a network of M identical processors, and we wish to run a program that will require a total of W seconds of work. In general, a program consists of multiple stages of work, each of which must be completed before the start of the next. For this paper we assume that the program has only one stage of work, and furthermore, we assume that the work in any stage is infinitely divisible, and therefore is always spread evenly among the available processors.

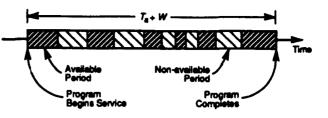

Each processor has a capacity of one second of work per second. A processor alternates between a nonavailable period, when someone is using it, and an available period, when it is sitting idle. We assume that the length of non-available periods is randomly distributed with mean  $t_n$  and variance  $\sigma_n^2$ , and that the length of available periods is also randomly distributed from a (possibly different) distribution with mean  $t_a$  and variance  $\sigma_a^2$ . We wish to run our program on the network of processors, using processors while they are in their available periods. The finishing time of the program is given by a random variable f, with probability distribution f(t), average  $\overline{f}$ , and Laplace transform  $F^{\circ}(s)$ . The purpose of this paper is to find

<sup>\*</sup>This work was supported by the Defense Advanced Research Projects Agency under contract MDA 903-82-C0064, Advanced Teleprocessing Systems, and contract MDA 903-87-C0663, Parallel Systems Laboratory.

f(t), or, in broader terms, to examine the potential use of currently wasted cycles. To do so, we examine a related function, w(u|t), the probability density function of the amount of work, u, completed by time t, which has mean  $W_t$  and variance  $Var[W_t]$ . Then, for a given W, f(t) is the distribution of the time for the completed work to first reach W, a point also known as the first passage time.

-

If the amount of work that we wish to do is small, relative to  $t_a$  and  $t_n$ , then the finishing time is highly dependent upon the states of the processors when the program arrives. If, for example, we have a small amount of work to do on a single processor, either the processor is available with no delay, or the processor is non-available, and we must wait, on average, t<sub>n</sub> seconds (assuming exponentially distributed nonavailable periods) before we can even start the work. If  $t_n$  is not small relative to W, then state of the processor when the program arrives strongly affects the finishing time distribution. In this paper, we use two techniques to mitigate the effect of this on the analysis. The single processor models make assumptions about the time that the program arrives (either in an available period or at the beginning of a non-available period). The multiprocessor model assumes that W is large relative to  $t_a$  and  $t_n$ , so the effect of initial conditions is negligible. Work is underway for the situations where W is not large.

Our analysis ultimately allows for arbitrary distributions of the lengths of available and non-available periods, but in our examples, we assume exponential distributions. Using the average available and non-available times measured by Mutka and Livny, the examples in this paper are generally based on the following parameters:  $t_a = 91$  minutes,  $t_n = 31.305$  minutes,  $W = 10^3$  minutes for single processor examples, and  $W = 10^4$  minutes for multiprocessor (M = 100) examples. We choose W large relative to  $t_a$  and  $t_n$  for the reasons mentioned in the previous paragraph.

We ignore communications overhead and task precedence issues in this paper, and assume that our program can use all available processors at any given time. The results of this paper, then, provide upper (i.e. optimistic) bounds on the best performance achievable in this situation.

In the remainder of this paper, we first discuss previous work by others, then analyze the problem for 1 processor. We find expressions for  $w(u \mid t)$  and f(t)in the single processor case. We then use  $w(u \mid t)$  to find f(t) for M processors and compare it to the single processor case.

## 3 Previous Work.

A single transient processor can be modeled in a variety of ways: as a priority queue, as a queue with vacations, as an unreliable system, or as a cumulative, alternating renewal process. Of these methods, we choose that last because it provides the asymptotic distribution of  $w(u \mid t)$  in a very simple form and for arbitrary available and non-available period distributions. We now briefly discuss the other alternatives.

#### 3.1 Preemptive Priority Queues.

We can model a transient processor using a preemptive priority queueing system with two classes. The high priority class represents non-available periods that interrupts the service of distributed programs, represented by the jobs in the low priority class. Such systems do not completely model a transient processor because high priority jobs continue to arrive while a high priority job is in service, and this represents a queueing of non-available periods. If we do not object to this, and if we assume that both available and nonavailable periods arrivals are from (different) Poisson processes, then the Laplace transform of the "completion time" (our  $F^*(s)$ ) is known [8], and from that we can get its mean and variance.

#### 3.2 Queues with Vacation.

Another model of a transient processor is a queueing system in which the server goes on vacations. In particular, we require that the vacations occur randomly and preempt any customer in service. If the available periods are exponentially distributed, Gaver [2] provides an analysis. For non-exponential available periods, Federgruen and Green [5] have analyzed such queues.

#### 3.3 Unreliable Systems.

Reliability analysis concerns itself with the availability of a system over time, and some work has been done to find the distribution of cumulative availability (the cumulative amount that a system is available over time). This corresponds exactly to accumulation of work in a network of transient processors. For a system with two states (available and non-available) Donatiello and Iver [4] find the transform of the cumulative availability, and they derive a closed-form expression when the time in each state is exponentially distributed. Using their results, we can find the moments of the amount of work done in a given amount of time for any specific available and non-available period distributions. However, we were unable to derive general results in terms of the distributions' moments, and therefore we turned to the cumulative, alternating renewal analysis described later in this paper. Although, their results do not directly provide the distribution of the first passage time, the transform of this may be obtained using techniques from the cumulative, alternating renewal analysis.

De Souza e Silva and Gail [3] discuss the calculation of cumulative availability in systems which can be modeled as homogeneous Markov chains. They find a general method for calculating cumulative availability, and further find good techniques for numerical evaluation of their method. The SAVE (System Availability Estimator) program [7] implements their method. For numerical, not approximate analytic, results, this is an excellent approach.

## 4 Results for One Processor.

We use two methods for deriving for the finishing time of a program on one processor. The first analysis provides the distribution of the first passage time with some restrictions on the distributions of the available and non-available periods (see section 4.1); however, it does not yield the distribution of the amount of work done over time. The second analysis, using a cumulative, alternating renewal process, provides us with the distribution of w(u|t) for arbitrary available and non-available period distributions, but only with the transform of the first passage time distribution. Given w(u|t) from the second analysis, we can then develop a model for M processors.

We may easily derive the averages  $\overline{W_t}$  and  $\overline{f}$ . In a long period of time, the processor spends, on average, a fraction  $t_a/(t_a + t_n)$  of its time in available periods. Thus in t seconds, the average amount of work completed is t times this fraction, or

$$\overline{W_t} = \frac{t_a}{t_a + t_n} t. \tag{1}$$

Because the processor completes, on average,  $t_a/(t_a + t_n)$  seconds of work per second, the reciprocal of this is the number of seconds it takes to complete one second of work. Multiplying this by W we find the average first passage time,

$$\overline{f} = \frac{t_a + t_n}{t_a} W. \tag{2}$$

If we wish to account for multiple processors, the average amount of work done per time period is increased by a factor of M, the number of processors, and the first passage time is likewise decreased by a factor of M, giving us:

$$\overline{W_t} = \frac{t_a}{t_a + t_n} M t. \tag{3}$$

and

$$\overline{f} = \frac{t_a + t_n}{M t_a} W \tag{4}$$

As we will find, this simple analysis accurately characterizes the system when our program takes a long time relative to the average length of the available and nonavailable periods.

#### 4.1 Direct Analysis.

Assume, for the moment, that we have only one processor (M = 1). If our program starts when the processor is available, as shown in Figure 1, it will finish at time  $W + \hat{w}$ , where  $\hat{w}$  is the *additional* (wasted) time the

Figure 1: Time for one processor to finish W seconds of work.

program spends in the system because the processor is sometimes in non-available periods.

Because the non-available periods are independent and identically distributed random variables with exponential distributions,  $P_{\psi}(t)$ , the probability distribution function of the additional time in non-available periods, given that we have *i* such periods, is an Erlang distribution; that is

$$\frac{dP_{\hat{w}}(t|i)}{dt} = \frac{(1/t_n)(t/t_n)^{i-1}}{(i-1)!}e^{-t/t_n}$$

(5)

The number of non-available periods that "arrive" during W seconds has a Poisson distribution with rate  $1/t_{\sigma}$ . Thus, unconditioning on this number, we get that the density of  $\hat{w}$  is

$$\frac{dP_{\hat{w}}(t)}{dt} =$$

$$\begin{cases} e^{-W/t_{\bullet}} u_{0}(t) & \text{if } t = 0 \\ \sum_{i=1}^{\infty} \frac{(1/t_{n})(t/t_{n})^{i-1}}{(i-1)!} e^{\frac{-t}{t_{n}}} \frac{(W/t_{0})^{i}}{i!} e^{\frac{-W}{t_{\bullet}}} & \text{if } t > 0 \end{cases}$$

(6)

where  $u_0(t)$  is a unit impulse at t = 0. For t > 0, this may be further reduced to

$$\frac{dP_{\hat{\boldsymbol{v}}}(t)}{dt} = \frac{1}{t_n} \sqrt{\frac{tW}{t_a t_n}} e^{-t/t_n} e^{-W/t_a} I_1(2\sqrt{\frac{tW}{t_a t_n}}) \quad (7)$$

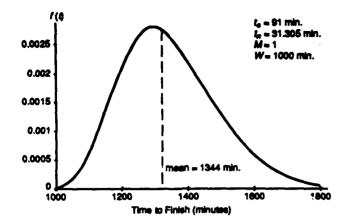

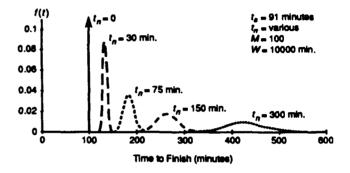

where  $I_1(z)$  is the modified Bessel function of the first kind of order 1. Figure 2 shows the distribution of the first passage time using  $t_a = 91$  and  $t_n = 31.305$ , and  $W = 10^3$ .

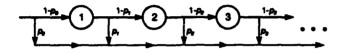

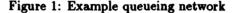

To find the mean and variance of this distribution, it simplifies the analysis to model the sequence of non-available periods using a series-parallel queueing server, shown in Figure 3, and then use known results for such servers. In this model, each of the infinite number of sub-servers (the numbered circles in the figure) has the same distribution as a single non-available period, and, in fact, represents a non-available period. We adjust the transition probabilities  $p_i$  so that the number of sub-servers a program passes through has the same distribution as the number of non-available periods arriving in W seconds. Upon entering the series-parallel server, the job immediately leaves the server with probability  $p_0$ , or the job enters sub-server

Figure 2: First Passage Time Density for Direct Analysis.

Figure 3: Series-parallel model of extra time needed to complete W seconds of work.

1 with probability  $1 - p_0$ . Then each time a job leaves a sub-server *i*, a similar choice is made between leaving the series-parallel server (with probability  $p_i$ ) or continuing on to the next sub-server (with probability  $1 - p_i$ ). For our purposes, we adjust the probabilities  $p_i$  so that the number of sub-servers passed through has a Poisson distribution. To compute these  $p_i$ , we note first that  $p_0 = e^{-t_* W}$ . For notational convenience, let  $\mathcal{P}_{\lambda}(i) = \frac{\lambda^*}{i!}e^{-\lambda}$ , the  $i^{th}$  term of a Poisson distribution with parameter  $\lambda$ . Next, we see that  $(1 - p_0)p_1 = \mathcal{P}_{W/t_*}(1)$ , and we immediately have that

$$p_1=\frac{\mathcal{P}_{W/t_*}(1)}{1-\mathcal{P}_{W/t_*}(0)}.$$

It may be proved by induction that

$$p_{i} = \frac{\mathcal{P}_{W/t_{\bullet}}(i)}{1 - \sum_{j=0}^{i-1} \mathcal{P}_{W/t_{\bullet}}(j)}.$$

(8)

Using these  $p_i$ 's, and the expression in Kleinrock [10] for  $\hat{W}^*(s)$ , the Laplace transform of the density of the time required to pass through a series-parallel server, we get

$$\hat{W}^{*}(s) = p_{0} + \sum_{i=1}^{\infty} \frac{(W/t_{e})^{i}}{s!} e^{-(W/t_{e})} \left(\frac{1/t_{n}}{s+1/t_{n}}\right)^{i} \quad (9)$$

which, after some manipulation, becomes

$$\hat{W}^*(s) = \mathcal{P}^*_{W/t_*}\left(\frac{1/t_n}{s+1/t_n}\right) \tag{10}$$

where  $\mathcal{P}_{\lambda}^{*}(z) = e^{\lambda(z-1)}$  is the z-transform of a Poisson distribution with parameter  $\lambda$ . We multiply this by  $e^{-Wz}$  to account for the W

We multiply this by  $e^{-W^{*}}$  to account for the W seconds that we are required to work, and finally find the transform for the distribution of time to finish W seconds of work, i.e.,

$$F^{*}(s) = e^{-Ws} e^{(W/t_{n})((1/t_{n})/(s+1/t_{n})-1)}.$$

(11)

Taking derivatives, we find that the mean time required to finish W seconds of work is

$$\overline{f} = W \frac{t_a + t_n}{t_a}, \qquad (12)$$

and the variance of this time is

$$\sigma_f^2 = 2 \frac{t_n^2 W}{t_a} \tag{13}$$

Note that Equation 12 agrees with Equation 2. This mean and variance may also be derived by viewing the distribution as a constant plus a random (Poissondistributed) sum of Erlang random variables, and using the well-known formulas for the mean and variance of a random sum of random variables [10].

We can modify this analysis for non-exponential non-available time distributions, but it still requires exponential available times so that the number of nonavailable periods in W seconds has a Poisson distribution. If we wish to allow arbitrary available period distributions as well, then we need a more sophisticated method of counting non-available periods, and this leads to analyzing the situation as a renewal process.

#### 4.2 Analysis as a Cumulative, Alternating Renewal Process

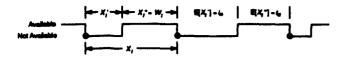

To allow arbitrary distributions for the available and non-available periods, we follow the presentation of Cox [1] in his treatment of cumulative, alternating renewal processes. As before, the single processor has a capacity of one second of work per second, and we wish to find the distribution of the time required for this processor to finish W seconds of work. Let  $X'_i$  be the duration of the  $i^{\text{th}}$  non-available period, and  $X''_i$ be the duration of the i<sup>th</sup> available period, as shown in Figure 4. Let the renewal points for our alternating renewal process be the beginning of the non-available periods, shown as heavy dots in the figure; the time between renewal points is then  $X_i = X'_i + X''_i$ . This has mean  $E[X] = t_a + t_n$  and variance  $Var[X] = \sigma_a^2 + \sigma_n^2$ . We assume that t = 0 occurs at the beginning of a renewal period.

To form a cumulative process from this, define  $W_i$ to be the amount of work completed in each renewal period:  $W_i = X_i''$ , with mean  $t_a$  and variance  $\sigma_a^2$ . Let  $Z_t$  be the sum of all the available time up to time t, excepting that in the current available period, if the

Figure 4: Cumulative Renewal Process

process is in such a period at time t.

$$Z_t = \sum_{i=1}^{N_t} W_i \quad (N_t = 1, 2, ...) \quad (14)$$

= 0 (N\_t = 0)

where  $N_t$  is the number of renewals in (0, t]. Asymptotically,  $Z_t$  has the same properties as  $w(u \mid t)$ , the process that accumulates the true total available time up to time t; however,  $Z_t$ 's analysis is more tractable than that of  $w(u \mid t)$ .

Cox's analysis allows the available and non-available periods to have arbitrary distributions. For t large,  $Z_t$ is the sum of many independent random variables, and it is asymptotically normal with mean

$$\mathbf{E}[Z_t] = \frac{t_a}{t_a + t_n} t \tag{15}$$

and variance

$$\operatorname{Var}[Z_t] = \frac{2(\sigma_a^2 t_n^2 + \sigma_n^2 t_a^2)}{(t_a + t_n)^3} t.$$

(16)

Using exponentially distributed available and nonavailable periods, these become:

$$\mathbf{E}[Z_t] = \frac{t_a}{t_a + t_n} t \tag{17}$$

$$Var[Z_t] = \frac{2(t_a t_n)^2}{(t_a + t_n)^3} t.$$

(18)

As noted before, the asymptotic properties of  $Z_t$  are identical to the asymptotic properties of w(u|t).

Comparing this to the result of the direct analysis, we note that for t equal to the mean first passage time (Eqn. 12), we have done, on average, W seconds of work, as we expected.

In his derivation, Cox, assuming that  $W_i$  is independent of  $X''_i$  for all i, derives a double transform for f(t). Unfortunately, this transform is very difficult to invert, but the asymptotic distribution of  $Z_t$  is really what we need so we can use it in the next analysis.

## 5 Results for M Processors

Because the amount of work done by one transient processor is the sum of a (possibly large) number of available periods, the total work done in time t is asymptotically normal with mean and variance given in Equations 17 and 18, respectively. If  $t_a \ll W$  and

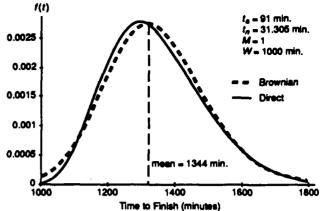

Figure 5: First Passage Time Distributions for Direct and Brownian Motion Analyses.

Figure 6: First Passage Time Densities for Brownian Motion Model for Various  $t_n$ .

$t_n \ll W$ , then it is reasonable to use Brownian motion as a model of an M processor system. All M processors are assumed to be independent, so the amount of work done by time t is the sum of M independent, (approximately) normally distributed random variables, with mean

$$\overline{b}t = \frac{t_a}{t_a + t_n} M t = p_a M t \tag{19}$$

and variance

$$\sigma_{b}^{2}t = \frac{2(\sigma_{a}^{2}t_{n}^{2} + \sigma_{n}^{2}t_{a}^{2})}{(t_{a} + t_{n})^{3}} Mt.$$

(20)

For exponential available and non-available distributions, Eqn. 20 becomes:

$$\sigma_{\delta}^{2}t = \frac{2(t_{a}t_{n})^{2}}{(t_{a}+t_{n})^{3}}Mt = \frac{2p_{a}^{2}(1-p_{a})Mt}{t_{n}}$$

(21)

where  $p_a = t_a/(t_a + t_n)$ .

With these as the parameters for our Brownian motion, the density of the time, t, that it takes for M

186

\_\_\_\_\_\_

· ....

Figure 7: First Passage Time Density for Brownian Motion Analysis.

processors to finish W seconds of work is well-known (e.g. see Karlin and Taylor [9]) and is given by:

$$f(t) = \frac{W}{\sqrt{2\pi\sigma_b^2 t^3}} \exp\left[-\frac{(W-bt)^2}{2\sigma_b^2 t}\right]$$

(22)

This has mean

$$\overline{f} = \frac{W}{\overline{b}} = \frac{W}{M} \frac{(t_a + t_n)}{t_a}$$

(23)

and variance

$$\sigma_f^2 = \frac{W}{\overline{b}} \frac{\sigma_b^2}{\overline{b}^2}.$$

(24)

and for exponential distributions, the latter becomes

$$\sigma_f^2 = \frac{2W}{M^2} \frac{t_n^2}{t_a}.$$

(25)

Equation 22 is the main result of this paper. Note that it makes no assumptions about the distributions of the available and non-available periods, except that their variances are finite, and only the distributions' means and variances appear in the first passage time.

Note that for the case M = 1, this mean and variance agree with our single processor analysis of section 4.1. The first passage time densities for both the single processor analysis and the multiprocessor analysis with M = 1 are shown in Figure 5.

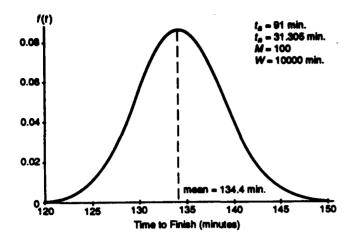

Figure 6 shows the distribution of first passage time for various  $t_n$  with  $t_a = 91$ , M = 100, and  $W = 10^4$ . Using the  $t_a = 91$  and  $t_n = 31.305$ , our job of  $10^4$ minutes would take about a week to run on a single, dedicated processor. When run on a network of 100 transient processors, it would take 134.06 minutes, or about 2.25 hours. The distribution of this first passage time is shown in Figure 7. Note that although  $W \gg t_a$ and  $W \gg t_n$ , we have that W/M, the finishing time if the processors were fully dedicated to the program, is

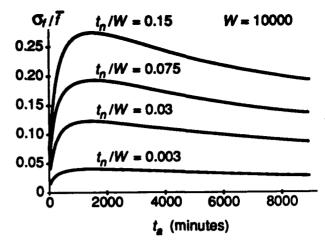

Figure 8:  $\sigma_f/\overline{f}$  with various  $t_a$  and  $t_n$ .

close to the average length of an available period, and it is remarkable that the curve is still so symmetrical.

It is useful to examine the ratio of  $\sigma_f$  to  $\overline{f}$ , namely:

$$\frac{\sigma_f}{\overline{f}} = \frac{\sqrt{\sigma_b^2}}{\sqrt{bW}} \tag{26}$$

to see what happens to the distribution as the parameters change. For exponential distributions this becomes

$$\frac{\sigma_f}{\overline{f}} = \sqrt{\frac{2t_n}{W}} \frac{\sqrt{t_n/t_a}}{1 + t_n/t_a},\tag{27}$$

and it is this equation that we examine in more detail. Figure 8 plots Eqn. 27 for fixed  $t_n$  and W, and varying  $t_a$ . Note that in this figure,  $t_n = 30$  minutes is the lowest line and  $t_n = 1500$  minutes is the uppermost line.

Because we assumed  $t_n \ll W$ , this ratio tends to be less than 1, reaching a peak when  $t_a = t_n$ . If we fix  $t_n/W$  and let  $t_n/t_a$  go to infinity (which implies  $t_a \rightarrow 0$ ), the ratio goes to 0. We explain this by noting that for small  $t_a$ , it takes very many available-nonavailable cycles before the work is finished. The law of large numbers insures that the first passage time distribution, which is the sum of these many periods, will then be tight about its mean.

If, on the other hand, we let  $t_a \rightarrow \infty$ , the ratio of the standard deviation to the mean goes to zero once again. When  $t_a$  is large relative to  $t_n$ , the nonavailable periods become negligible, as if the processors are always available. Again, the first passage time distribution becomes very tight about its mean because non-available time periods add little variability to the finishing time.

Given that the first passage time distribution is tight about its mean, (i.e.  $t_a \gg t_n$ , or  $t_a \ll t_n$ , or  $W \gg t_n$ ), it may be accurate enough to consider the distribution as an impulse at the mean finishing time (in the spirit of the law of large numbers). Using the previous example again, we find  $\sigma_f^2 = 21.53$ , and approximating f(t) as a normal distribution (discussed below), we find that 90% of the time, programs requiring  $10^4$ minutes of work will finish within 7.6 minutes of the 134.4 minute mean finishing time.

The central-limit theorem says that f(t) will tend toward a normal distribution when many available non-available periods occur before the program completes (i.e.  $W \gg t_a$  and  $W \gg t_n$ ). To approximate the first passage time, we use a normal distribution with the same mean and variance as the first passage time distribution:

$$\hat{f}(t) = \frac{1}{\sqrt{2\pi\sigma_f^2}} e^{-(t-\overline{f})^2/(2\sigma_f^2)}$$

(28)

When the mode of the first passage time distribution is close to its mean, a normal distribution well approximates the first passage time. The mode is:

$$t_{mode} = \frac{1}{2} \sqrt{\frac{9(\sigma_b^2)^2}{\overline{b}^4} + \frac{4W^2}{\overline{b}^2} - \frac{3\sigma_b^2}{2\overline{b}^2}}.$$

(29)

Comparing this to the mean, we find that the percentage difference between the two is approximately  $3\sigma_b/2bW$ , which, as we would expect, shrinks as W grows.

## 6 Conclusion

We have analyzed a network of transient processors, and determined the probability density of the length of time it takes to finish a fixed amount of work. The main result for an M processor network is given in Equation 22, and it is valid for general available and non-available period distributions. Simulations confirm that Brownian-motion-with-drift is an accurate model of system performance under the assumptions given above. With large programs that run for a long time relative to the length of available and non-available periods, the central limit-theorem applies, and the Brownian-motion-with-drift model remains good regardless of the distributions of the available and the non-available periods. Under these assumptions, the distribution of finishing time will be very tight about its mean, and is well approximated by a normal distribution.

It does remain to account for communication overhead and precedence relationships, but it is likely that these can be accommodated, or at least approximated, within the model.

The analysis in this paper has not examined the effect of multiple programs in the network. We may now use the first passage time distribution (Eqn. 22), as the service time in a queueing system that represents the network. If each job gets the whole network and they must queue, then a G/G/1 queue is a good model. If all the programs in the network share the processors equally, then we could model the network as an M/G/1 processor-sharing system. The analysis of such systems remains for a future paper.

It is well known that, for a given total processing capacity, the average response time is shortest if we use one large processor rather than many small processors [11]. From this perspective, the trend toward individual workstations is a curious one. However, this result assumes that each program executes on only one processor. If we distribute the program over all the small processors, then we may recover, at least partially, the response time advantages of a large, central system, while retaining the advantages of individual workstations.

## References

- [1] D. R. Cox. *Renewal Theory*. Methuen and Co., Ltd., London, science paperbacks edition, 1962.

- [2] Jr. D. P. Gaver. A waiting line with interrupted service, including priorities. Journal of the Royal Statistical Society, B24:73, 1962.

- [3] Edmundo de Souza e Silva and H. Richard Gail. Calculating Availability and Performability Measures of Repairable Computer Systems Using Randomization. Journal of the ACM, 36(1):171-193, January 1989.

- [4] Lorenzo Donatiello and Balakrishna R. Iyer. Closed-Form Solution for System Availability Distribution. *IEEE Transactions on Reliability*, R-36(1):45-47, April 1987.

- [5] A. Federgruen and L. Green. Queueing Systems with Service Interruptions. Research Working Paper 84-5, Columbia University, 1984.

- [6] Robert Felderman, Eve Schooler, and Leonard Kleinrock. The Benevolent Bandit Laboratory: A Testbed for Distributed Algorithms. *IEEE Journal on Selected Areas in Communications*, 7(2):303-311, February 1989.

- [7] Ambuj Goyal. System Availability Estimator (SAVE) User's Manual Version 2.0 (External). Technical Report RC 12517 (No. 56267), IBM Watson Research Center, February 1987.

- [8] Daniel P. Heyman and Matthew J. Sobel. Stochastic Models in Operations Research, Volume 1: Stochastic Processes and Operating Characteristics. Series in Quantitative Methods for Management. McGraw Hill, 1982.

- [9] Samuel Karlin and Howard M. Taylor. A First Course in Stochastic Processes. Academic Press, second edition, 1975.

- [10] Leonard Kleinrock. Queueing Systems, Volume 1: Theory. John Wiley and Sons, 1975.

- [11] Leonard Kleinrock. Distributed Systems. Communications of the ACM, 28(11):1200-1213, November 1985.

.

[12] Willard Korfhage. Distributed Systems and Transient Processors. PhD disservation, University of California, Los Angeles, 1989.

· ....

4

- [13] Matt W. Mutka and Miron Livny. Profiling Workstation's Available Capacity for Remote Execution. Computer Sciences Technical Report 697, CS Dept., Univ. of Wisconsin, May 1987.

- [14] David A. Nichols. Using Idle Workstations in a Shared Computing Environment. In Proceedings of the Eleventh ACM Symposium on Operating System Principles, pages 5-12. ACM, November 1987.

## On Parallel Processing Systems: Amdahl's Law Generalized and Some Results on Optimal Design

Leonard Kleinrock, Fellow, IEEE, and Jau-Hsiung Huang

Abstract-We model a job in a parallel processing system as a sequence of stages, each of which requires a certain integral number of processors for a certain interval of time. With this model we derive the speedup of the system for two cases: systems with no arrivals, and systems with arrivals. In the case with no arrivals, our speedup result is a generalization of Amdahl's Law. We extend the notion of "power" (the simplest definition is power = throughput/response time) as previously applied to general queueing and computer-communication systems to our case of parallel processing systems. With this definition of power we are able to find the optimal system operating point (i.e., the optimal input rate of jobs) and the optimal number of processors to use in the parallel processing system such that power is maximized. Many of the results for the case of arrivals are the same as for the case of no arrivals. A familiar and intuitively pleasing result is obtained, which states that the average number of jobs in the system with arrivals equals unity when power is maximized.

We also model a job in a way such that the number of processors required is a continuous variable that changes continuously over time. The same performance indices and parameters studied in the discrete model are evaluated for this continuous model. These continuous results are more easily obtained, are easier to state, and are simpler to interpret than for the discrete model.

Index Terms—Amdahi's Law, multiprocessing, optimal design, parallel processing, power, processor efficiency, speedup, system utilization.

#### I. INTRODUCTION

S parallel computing systems proliferate, the need for effective performance evaluation techniques becomes ever more important. In this paper, we study certain fundamental performance indices, namely, *speedup*, *response time*, *efficiency*, and *power*, and solve for the optimal operating point of these systems. Specifically, by maximizing "power," we are able to find the optimal input rate of jobs and the optimal number of processors to use, given a characterization of the workload.

We model a parallel processing system as a system with a single queue of waiting jobs. Our first model (in Section IV) assumes that only a single job needs to be processed. Our second model (in Section V) allows a stream of arrivals to enter the system; however, only one job may be admitted

J.-H. Huang is with the Department of Computer Science and Information Engineering, National Taiwan University, Taipei, Taiwan.

IEEE Log Number 9105395.

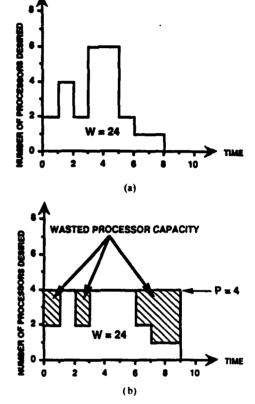

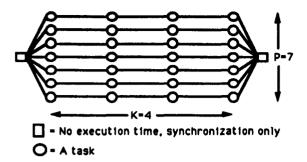

Fig. 1. Job profile. (a) Unlimited number of processors. (b) Limited number of processors (P = 4).

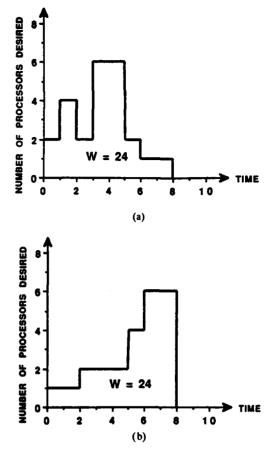

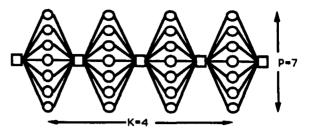

into service at a time, following a FCFS discipline, while the others wait in the queue. Both models deal with jobs as follows. While in service, the system provides a maximum of P parallel processors to work on the job. A job is modeled as a sequence of independent stages which must be processed, where the number of processors desired by the job in each stage may be different. If, for some stage, the job in service requires fewer processors than the system provides, then the job will use all that it needs and the other processors will be idle for that stage. If, for some other stage, the job in service requires more processors than the system provides, then it will use all the processors in the system (in a processor sharing fashion [10]) for an extended period of time such that the total work served in that stage is conserved. An example is given in Fig. 1 in which the total processing work required by a job is W = 24 s. In this example, if  $P \ge 6$ , then it takes 8 s to complete the job as shown in Fig. 1(a), whereas if only P = 4 processors are provided, then it takes 9 s as shown in

0098-5589/92\$03.00 C 1992 IEEE

Manuscript received April 1, 1991; revised September 20, 1991. Recommended by E. Gelenbe. This work was supported by the Defense Advanced Research Projects Agency, Department of Defense under Contract MDA903-87-C-0663.

L. Kleinrock is with the Computer Science Department. University of California, Los Angeles, Los Angeles, CA 90024.

Fig. 1(b), in which case 12 s of processor capacity are wasted.

The model described above has been highly idealized. In particular, we are neglecting some of the following important aspects of the workload. First, we do not allow general precedence relations among the tasks. Our precedence structure is equivalent to a series-parallel task graph with deterministic task service times (see [6] for the definition of the task graph model of computation). Second, we do not separately model the communication times between tasks (i.e., the interprocess communication overhead). We hasten to point out that incorporating this overhead is not simply a matter of adding additional time to each task's processing time, since such overhead only occurs when a task on one processor must pass its results to a task on a different processor; thus to properly include interprocess communication costs, one must model the way in which tasks are assigned to processors (i.e., the task partitioning problem), an assignment that we choose to neglect. Third, we ignore I/O communication overhead related to the management and execution of parallel programs. Lastly, we assume that the program structure is infinitely divisible, in that the time to execute w units of work is equal to max (w/P, w/P'), where P is the number of processors that the system provides for execution of this work, and P' is the maximum number of processors that the program is able to use for this work (i.e., the parallelism for this work). These assumptions simplify our analysis and lead to idealized results.

Our workload model was first reported by us in [8]. Later, Gelenbe [6] described a very similar model, as did Sevcik [15]. Gelenbe extended his model, which he referred to as the "Activity Set Model," to include the effect of inefficient use of processors, imbalance of the workload among the processors, and interprocess communication times. Sevcik also described ways in which this idealized model could be extended to include the effect of I/O communications, overhead, and dependencies among parallel threads assigned to different processors.

For such a parallel processing system there are two performance measures which compete with each other: processor efficiency and mean response time. One can increase the processor efficiency of the system (by reducing the number of processors), but then the mean response time will also be increased. Similarly, one can lower the mean response time (by increasing the number of processors), but then the processor efficiency of the system will also be lowered. In this paper these two performance measures are combined into a single measure, known as power, which increases by either lowering the mean response time or by raising the processor efficiency of the system. We seek to find that number of processors which maximizes power.

Power, studied in [5], [11], and [12], was defined for a general queueing system in [12] as

$$\frac{\rho}{T/2}$$

where  $\rho$  is defined as the system utilization, T is defined as the mean response time, and  $\overline{x}$  is defined as the average service time. With this measure we see that an increase in system utilization ( $\rho$ ) or a decrease in response time (T) increases

the power. (Note that this normalized definition is such that since  $0 \le \rho < 1$ , and since  $1 \le T/\bar{x}$ , then  $0 \le$  power < 1.) The symbol "\*" will be used throughout to denote variables which are optimized with respect to power. In [12] it was found that for any M/G/1 queueing system [9], power is maximized when  $\bar{N}^* = 1$ , where  $\bar{N} =$  the average number of jobs in the system. This result says that an M/G/1 system has maximum power when on the average there is only one job in the system. This result is intuitively pleasing, since it corresponds to our deterministic reasoning that the proper operating point for a single-server system is exactly when only one job is being served in the system and no others are waiting for service at the same time. In this paper, our results also show that  $\overline{N}^* = 1$ when power is maximized with respect to the job arrival rate  $(\lambda)$ .

One might argue that power, as here defined, is an arbitrary performance measure. In response to this argument we point out that one can generalize the definition of power in a way which allows the reader to emphasize delay (or efficiency) in a variety of ways so as to match his or her needs. This issue is discussed below in Section II as well as in [5] and [12]. Moreover, other researchers have seen fit to optimize power for models similar to ours (see, for example [4]). An extensive study of power applied to computer networks is given in [5].

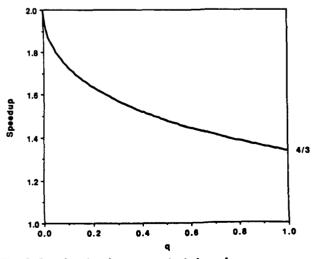

An alternative, and much more familiar, performance measure for parallel processing systems is speedup, which describes how much faster a job can be processed using multiple processors, as compared to using a single processor. Specifically, speedup is the ratio of the mean response time of a job processed by a single processor to that of a job executed in a parallel processing system with, say, P processors. Speedup and power are related and we discuss how they interact throughout this paper. Eager et al. [4] also discuss issues similar to those in this paper. Their focus is on estimating speedup and efficiency (for the no arrivals case only) simply from the value of the "average parallelism," which is defined as W, the total processing work required by a job, divided by the time it would take to service the job if there were an unlimited number of processors available; in Fig. 1(a) we have W = 24, and service time = 8, giving an average parallelism equal to 3. They also use the definition of power as we had defined in [11] and [12] and obtain the same result as we obtain in Corollary 7 below. They consider the case of deterministic workloads. Gelenbe [6] introduced an alternate model for the workload for which he also calculates speedup in the case of an infinite number of available processors. He models a job as having a random task graph in which the density of precedence relations between tasks is given by  $p (0 \le p \le 1)$ ; he then derives an approximation for an upper bound on the speedup; namely, (1 + p)/2p.

#### **II. DEFINITIONS**

We have already defined the following:

- P = Number of (identical) processors in the server,

- W = Average number of seconds required to process a job on a single processor; and

- $\overline{N}$  = Average number of jobs in the system.

Moreover, we now define the following additional quantities:

- $\overline{x}(P) =$  Mean service time of a job in a *P*-processor system (note that the maximum mean service time is  $\overline{x}(1) = W$  and that the minimum mean service time is  $\overline{x}(\infty)$ );

- $T(\lambda, P) =$  Mean response time (queueing time plus service time) of a job in a queueing system with an input rate  $\lambda$  and P processors;

- $\lambda$  = arrival rate of jobs;

- $\rho$  = system utilization; i.e., the fraction of time when there is at least one job in the system.

$$= \lambda \overline{x}(P);$$

and

u(P) = processor efficiency in a P-processor system.

Note the difference between u(P), which is the average processor efficiency given P processors, and  $\rho$ , which is the average system utilization. Whenever there is a job in the system, the system utilization is "1," but the processor efficiency need not be "1" in that case, since there may be some idle processors (i.e., it may be that the job in service does not require all the processors). Hence the system utilization is always greater than or equal to the processor efficiency. (Note that  $u(1) = \rho$  for a single processor queueing system.)

Two cases regarding the number of jobs in the system are considered in this paper. Case one allows no arrivals of additional jobs (Section IV). That is, there is only one job in the system, and we are concerned with  $\overline{x}(P)$ , its mean service time in a *P*-processor system. Case two allows jobs to arrive from a Poisson process at a rate  $\lambda$ , and so queueing effects are considered (Section V).

For the first case, we define the (no arrivals case) speedup with P processors, denoted by  $S_n(P)$ , to be

$$S_n(P) = \frac{\overline{x}(1)}{\overline{x}(P)} = \frac{W}{\overline{x}(P)}.$$

Note that

$$1 = \frac{W}{\overline{x}(1)} \le S_n(P) \le \frac{W}{\overline{x}(\infty)}.$$

Thus it is natural for us to define the maximum value for speedup  $S_{n,max}$  as follows:

$$S_{n,\max}=\frac{W}{\overline{x}(\infty)}.$$

Furthermore, we see that  $S_{n,\max}$  = average parallelism.

For the second case, we define the (arrivals case) speedup with P processors at system utilization  $\rho$ , denoted by  $S_a(\lambda, P)$ , to be

$$S_a(\lambda, P) = \frac{T(\lambda, 1)}{T(\lambda, P)}$$

We must distinguish the processor efficiency u(P) in these two cases as follows:

- $u_n(P) =$  processor efficiency given P processors in the no arrivals case; and

- $u_a(\lambda, P) =$  processor efficiency given job arrival rate  $\lambda$ and P processors in the case with job arrivals.

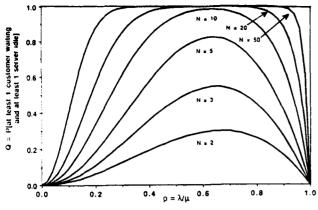

We now introduce the appropriate definitions of *power*, which we denote by the symbol Q (we would prefer to use the obvious notation P, but P has already been used to denote the number of processors). Let

$Q_n(P) =$  power given P processors in the no arrivals case; and

$Q_{a}(\lambda, P) =$  power given a job arrival rate  $\lambda$  and P processors in the case with job arrivals.

In this paper we are concerned mostly with power which is defined as processor efficiency divided by the mean response time.

In the case of no arrivals, the mean response time of the (single) job is simply its mean service time  $\overline{x}(P)$ , and so:

$$Q_n(P) = \frac{u_n(P)}{\overline{x}(P)}.$$

Clearly, power will increase by either raising the processor efficiency or by lowering the mean service time. A more general definition of power (as originally introduced in [12]) is given as

$$Q_n^{(r)}(P) = \frac{\left[u_n(P)\right]^r}{\overline{x}(P)}$$

where r is a positive real number whose value may be selected by the system designer. With this generalization, a designer may express a stronger preference for an increase in the processor efficiency at the expense of an increase in the mean service time by simply increasing the value of the parameter r (and vice-versa). Note that  $Q_n(P) = Q_n^{(1)}(P)$ .

In the case of job arrivals, the definition of power becomes:

$$Q_a(\lambda, P) = \frac{u_a(\lambda, P)}{T(\lambda, P)}$$

and the generalization in this case is

$$Q_a^{(r)}(\lambda, P) = \frac{\left[u_a(\lambda, P)\right]^r}{T(\lambda, P)}$$

where again r is a positive real number to be used as a degree of freedom by the system designer. Note that  $Q_a(\lambda, P) = Q_a^{(1)}(\lambda, P)$ .

With these definitions of power, our goal is to find the optimal number of processors to use in a parallel processing system such that power is maximized. Furthermore, in the case of job arrivals, we also seek the optimal system operating point (i.e., the optimal input rate of jobs).

The rest of this paper is organized as follows. In Section III we present two models of a job: a discrete model, and a continuous model. In Section IV we solve the case when no arrivals are allowed in the system. In this case we find the speedup of the system given P processors. We also find  $P^*$ , the number of processors which maximizes power. In Section V we solve the case when job arrivals are allowed in the system given P processors. We also find  $\lambda^*$  and  $P^*$ , which maximize power. One interesting result we get is that the  $P^*$  for systems with no arrivals and the  $P^*$  for systems with arrivals are equal when power is maximized; this provides a simplification in system design.

#### III. WORKLOAD MODELS

We consider both a discrete as well as a continuous model of job requirements.

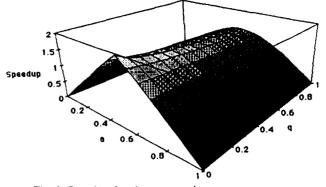

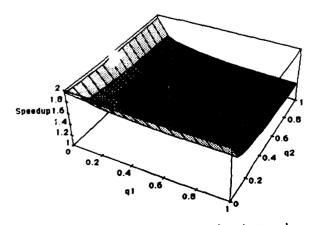

#### A. A Discrete Job Model